On appelle un processeur CISC, Complex Instruction Set Computer, un processeur disposant d'un nombre important d'instructions (plus de 300 pour un 68HC11 de Motorola)

Or statistiquement, 80% des traitements des langages de haut niveau font appel à 20% d'instructions, d'où l'idée de développer des processeurs ayant moins d'instructions mais dont le traitement est optimisé.

Ces processeurs RISC, Reduced Instruction Set Computer, ont été développé par Microchip avec les microcontrôleurs PIC ou par IBM avec les PowerPC, SPARC ou Alpha.

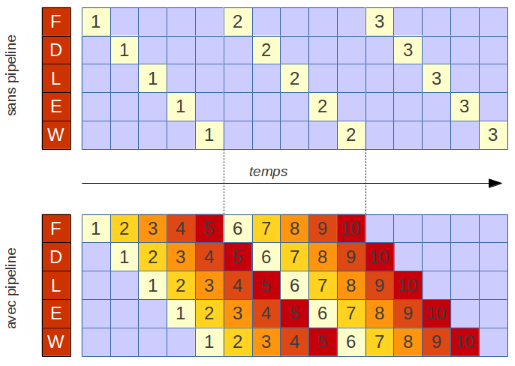

L'optimisation est obtenue par l'usage de nombreux registres internes et des méthodes de pipelining.

F:fetch; D: Decode; L: load; E:Execute; W:write

(sources Jean-Michel Richer - Université d'Anger)

Actuellement, la plupart des processeurs CISC utilisent des principes d'optimisation du RISC.